次世代半導体ガラス基板への微細レーザー加工を実現

東京大学

発表のポイント

- 次世代半導体の回路基板と目されているガラス基板に対し、直径10マイクロメートル以下の微細穴あけ加工を深紫外レーザーで実現しました。

- 深紫外領域の超短パルスレーザーを用いることで、ガラス基板に対し、配線用に利用可能な細く長い(高アスペクト比)穴あけ加工を高密度にできることを実証しました。

- 今後さらなる微細化と高アスペクト比化そして高速化を実現することで、半導体製造の後工程において材料と加工技術における日本のプレゼンス向上が期待されます。

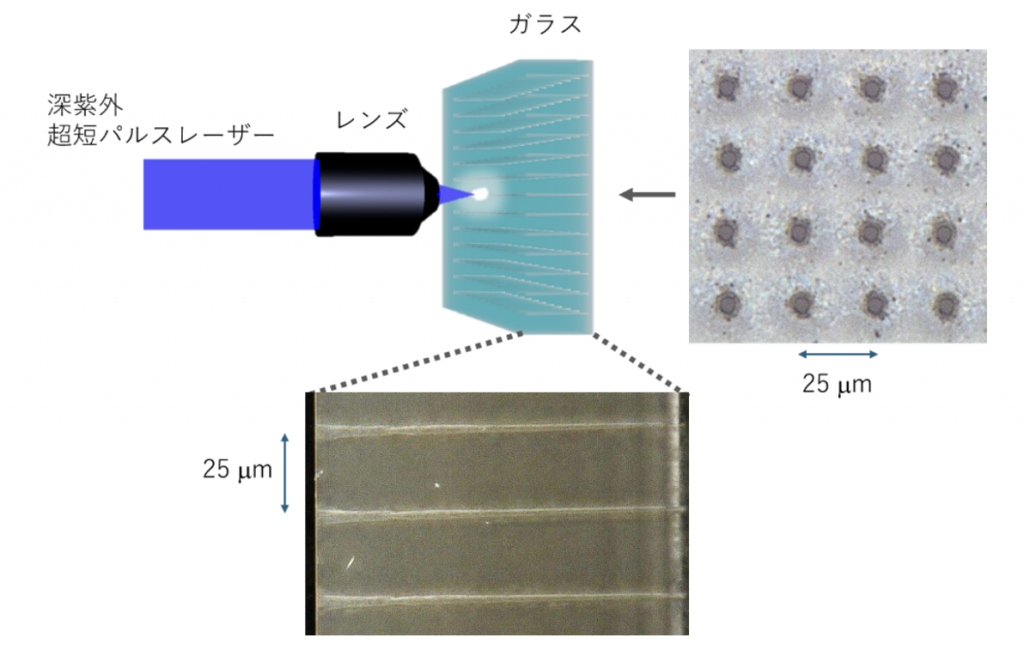

次世代半導体の基板に用いられると期待されているEN-A1ガラスに対して、25マイクロメートル間隔で直径10マイクロメートル以下の穴あけ加工を深紫外レーザーで実現しました

概要

EN-A1ガラスに対し、深紫外レーザーを照射することで直径10マイクロメートル以下の穴を25マイクロメートル間隔であけました。高密度に穴あけをしても割れることなく高アスペクト比の穴あけ加工が可能であることを実証しました。

国立大学法人東京大学(総長 藤井 輝夫)は、半導体基板用ガラスへの極微細レーザー穴あけ加工技術を開発しました。今回用いたガラス基板はAGC株式会社より提供されたEN-A1(注1)で、次世代の半導体製造「後工程」(注2)に用いられる候補材料の一つです。本研究で開発された手法を用いると、レーザーのみで直径10マイクロメートル以下、アスペクト比(注3)が20程度の微細な穴あけができ、従来のエッチングによる穴あけよりも高いアスペクト比の加工ができます。

この成果は今後生成AI等に必要なハイパフォーマンスコンピュータやデータセンター用のチップレット(注4)において、回路基板の材料がガラスに移行する際に役に立つと期待されます。本研究グループは今後も産業界と連携して、半導体パッケージ基板のさらなる微細化や高品位化を目指し、次世代半導体産業における日本の競争力強化に貢献してまいります。

本成果の技術に関する詳細は、2025年5月27日からアメリカ・ダラスで開催される国際会議ECTC2025で報告されました。

全文PDF発表内容

発表の背景

露光技術の進歩に伴い、半導体チップは微細化するとともに大面積化も進んでいます。それとともに、半導体チップを実装する回路基板の配線も微細化と大面積化が求められています。さらにはbeyond 5Gや6Gの通信のために高周波化も重要となってきています。従来回路基板には樹脂が用いられていましたが、これらの要求に応えるために、基板の材料が樹脂からガラスへと移行するとされています。ガラスは高周波特性が良く、大面積で平坦、そしてシリコンと熱特性を合わせることができるといった特徴があります。回路基板には表と裏をつなぐ配線のために多数の貫通穴をあける必要がありますが、高密度の配線のためには微細な穴が必要となります。ところがガラスは脆性材料であるため、極端に小さな径で深い穴を真っ直ぐ精密にあけることは、ひび割れなどの問題があり大変困難です。ガラスの微細穴あけには大きく分けて、化学的なエッチングを使う手法とレーザーで穴あけをする手法がありますが、双方利点と欠点があり、いずれも確立した技術とはなっていません。そこで現在世界中でガラスへの微細かつ高アスペクト比の穴あけ加工技術の研究開発が行われています。

発表の内容

この度、本研究開発チームでは半導体基板として電気的・熱的特性が優れているEN-A1ガラスに対してレーザー加工のみで微細貫通穴加工を行いました。

超短パルスの深紫外レーザーを用いることで、ガラスに直径10マイクロメートル以下の穴を貫通させることができました。アスペクト比にするとおよそ20程度です。これまで、酸を使うエッチングでは高アスペクト比を実現することが困難でしたが、深紫外レーザーによる直接加工ではクラックがなく、高アスペクト比を実現できることが分かりました。本加工は化学処理を一切伴わないため廃液処理などの環境負荷も低減できます。

これは次世代半導体製造の後工程において基板のコア材やインターポーザ(注5)をガラスへと移行する際に貫通穴をあける技術として、重要なマイルストーンとなるものです。この技術は今後半導体のさらなる微細化や複雑化するチップレット技術において貢献することが期待されます。

関連情報:

発表者・研究者等情報

- 東京大学

- 物性研究所

- 小林 洋平 教授 <兼:同大学光量子科学連携研究機構>

- 乙津 聡夫 特任研究員

- 遠藤 翼 特任研究員

- 大学院理学系研究科附属 フォトンサイエンス研究機構

- 田丸 博晴 特任教授 <兼:同大学光量子科学連携研究機構>

- 物性研究所

- AGC株式会社

- 電子カンパニー ASPプロジェクト 技術開発グループ

- 佐藤 陽一郎

- 技術本部 先端基盤研究所 機能化プロセス部

- 柴田 章広

- 電子カンパニー ASPプロジェクト 技術開発グループ

学会情報

- 学会名:ECTC(2025 IEEE 75th Electronic Components and Technology Conference)

- 題 名:High-aspect-ratio, 6-μm-diameter through-glass-via fabrication into 100-μm-thick EN-A1 by dry laser micro-drilling process

- 著者名:Toshio Otsu, Tsubasa Endo, Akihiro Shibata, Yoichiro Sato, Hiroharu Tamaru and Yohei Kobayashi

- URL:https://www.ectc.net/program/75-ECTCFinal-Web.pdf

研究助成

本研究の一部は、光・量子飛躍フラッグシッププログラム(Q-LEAP)(課題番号:JPMXS0118067246)により実施されました。(2025/6/19 課題番号追記)

用語解説

- (注1)EN-A1:

- AGC株式会社が提供する半導体回路基板用のアルカリフリーガラスの一つ。熱膨張係数がシリコンと近いためにシリコンチップを載せたときに反りが小さくなる。

- (注2)半導体後工程:

- 半導体製造工程のうちチップを作成するのが前工程、チップを実装するのが後工程。

- (注3)アスペクト比:

- 縦と横の比。穴あけの場合は深さと直径との比を表す。

- (注4)チップレット:

- 従来は一つのチップでロジック構成要素を一体で製造していたが、チップの大面積化に伴い歩留まりが悪くなってきた。チップレットとは、構成要素ごとに別チップとして製造した上で、パッケージ基板上に組み合わせて実装し一体のパッケージとして動作するよう製造する技術およびその手法。チップレット化により、後工程も含めて半導体の性能向上が期待されている。

- (注5)インターポーザ:

- チップ間やチップと回路基板とをつなぐための中間的な基板。微細な配線と貫通穴からなる。チップレットなどの先端半導体パッケージに不可欠となってきている。

関連ページ

- 東京大学物性研究所 小林研究室

- 2024.05.31プレスリリースDUVレーザーで半導体基板に世界最小の穴あけ加工を実現 ―4法人で半導体後工程技術を開発―

- 2022.10.24プレスリリース次世代半導体製造向けの極微細穴あけ加工を実現 ―業種横断の協働拠点で先端半導体をけん引―

- 2021.03.01物性研ニュースNEDOの事業成果を集約したプラットフォームを構築 ―レーザー光源や加工機を連携させ、最適な加工条件を探索―

- 2018.10.23プレスリリース極端紫外線レーザーにより熱影響が極めて少ない材料加工を実現 -レーザー加工メカニズムの解明や最適加工の実現に期待-

- 2017.11.27プレスリリース「TACMIコンソーシアム」を設立 -産官学連携で光ものづくり協創を目指す-