DUVレーザーで半導体基板に世界最小の穴あけ加工を実現 ―4法人で半導体後工程技術を開発―

東京大学 味の素ファインテクノ株式会社 三菱電機株式会社 スペクトロニクス株式会社

発表のポイント

- 次世代半導体基板加工技術として不可欠な、深紫外(DUV)レーザー加工機を用いた層間絶縁膜への直径3マイクロメートルの微細穴あけ加工を実現しました。

- 現在チップ実装基板の層間配線として用いられているのは、直径40マイクロメートル穴であり、一桁小さい微細穴あけ加工技術の実現は、半導体実装基板の高密度化へ貢献します。

- 半導体後工程におけるレーザー微細穴あけ加工技術の向上により、次世代チップレットの高機能化が期待されます。

概要

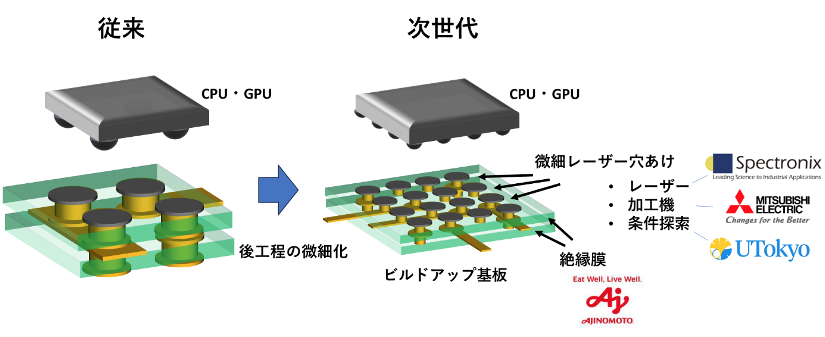

国立大学法人東京大学(総長 藤井 輝夫 以下、東京大学)、味の素ファインテクノ株式会社(代表取締役社長 真子 玄迅 以下、味の素ファインテクノ)、三菱電機株式会社(執行役社長 漆間 啓 以下、三菱電機)、スペクトロニクス株式会社(代表取締役社長 長岡 由木彦 以下、スペクトロニクス)はこのたび、次世代の半導体製造「後工程」(注1)に必要な、パッケージ基板(注2)への3マイクロメートルの極微細レーザー穴あけ加工技術を開発しました。既存技術より一桁小さい穴あけ加工技術を確立することで、より高密度な基板間配線が実現し、今後生成AI等に必要なハイパフォーマンスコンピュータやデータセンター用のチップレット(注3)の発展に役立つことが期待されます。

本成果は、東京大学が運用している「TACMIコンソーシアム(注4)」において、企業と大学が業種を越えて連携したことにより、実現しました。4法人は今後も連携して、半導体パッケージ基板のさらなる微細化や高品位化を目指し、次世代半導体産業における日本の競争力強化に貢献してまいります。

本成果の技術に関する詳細は、2024年5月28日からアメリカ・デンバーで開催されている国際会議ECTC2024で報告されました。

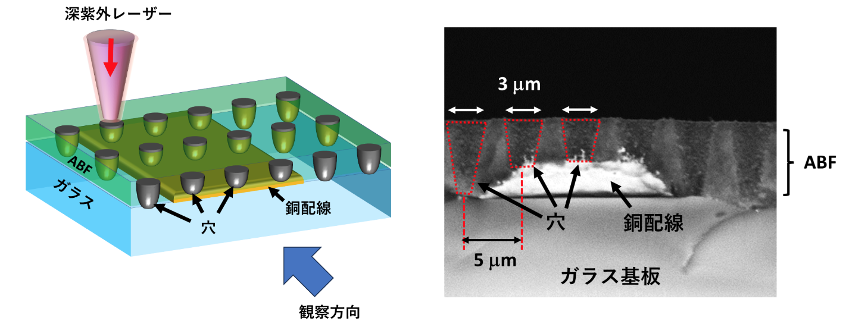

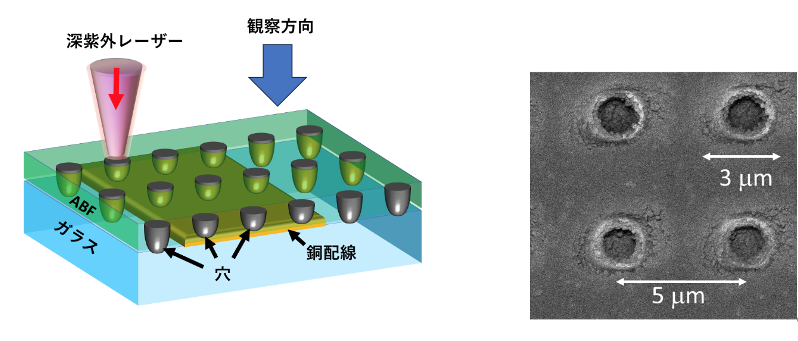

左図に示すように、ガラス基板の上に一部銅の配線を配置し、その上に3マイクロメートル厚のABFを作成。上からDUVレーザーを用いて5マイクロメートル間隔で直径3マイクロメートルの穴をあけました。右図の電子顕微鏡写真のように、現在の実装技術よりも一桁程度小さい穴をあけることができました。

発表内容

発表の背景

近年、EUV露光(注5)技術の発展により半導体チップの微細化が進み、チップの電極間隔も小さくなってきています。それに伴い、チップを受ける側のパッケージ基板の配線も微細化が進んでいます。基板は多層構造となっており、層間の電気信号は絶縁層にあけられた微小な穴を通して結合されます。現在は40マイクロメートル程度の穴をレーザーであけて金属メッキを施すことで層間配線を行っていますが、チップの微細化に伴い将来パッケージ基板の穴径において5マイクロメートル以下の微細化が必要とされています。しかしながら現在用いられているレーザー加工技術では、レーザーや光学系の特性で小さい径に集光することが困難であり、また高いアスペクト比の穴あけ加工はできないという問題がありました。また、これに対応する微細穴あけ加工に適した薄い絶縁層も必要でした。

発表の内容

この度、本研究開発チームではTACMIコンソーシアムにおいて、レーザー開発、加工機開発、材料開発およびパラメータ探索を得意とする4法人が技術を持ち寄ることにより、これらの課題を解決し、半導体向けの層間絶縁体として極めて高いシェアを占める味の素ビルドアップフィルムⓇ(ABF)(注6)に3マイクロメートルという超微細穴あけ加工を実現しました。

東京大学はガラス基板上に銅を蒸着したのちに、レーザー加工により銅をパターン状に削り取り、微細な銅の配線を作成しました。味の素ファインテクノが前記銅配線層上に薄膜ABFを積層することで銅上に3マイクロメートルの絶縁層を形成しました(図1左)。スペクトロニクスは波長266ナノメートルのDUV高出力レーザーを担当し、三菱電機は深紫外線用に特別に開発したレーザー加工機の光学系の工夫を行い、集光サイズを従来よりも小さくする改良を行いました。東京大学でAIを活用した条件探索を行った結果、エッチング技術を用いることなくレーザー加工のみで3マイクロメートル直径の穴をABF上に作成することができました(図1右および図2右)。図2右を見ると、ABFにのみ穴があき、下の銅配線やガラスは削れていないことが分かります。この技術を用いると、自由な穴あけパターンを基板上に高速に作成することができます。

今後の展望

本成果は、半導体業界における後工程ロードマップにおいて重要なマイルストーンとなるものです。レーザー加工機で次世代の微細穴あけ加工が可能であることを示したことで、半導体のさらなる微細化において、低コストで自由度の高い基板加工が可能であることが分かりました。今後さらなる微細化に取り組むとともに、複雑化するチップレットの製造工程における技術課題について、レーザー加工で対応可能な範囲を拡大するための研究・技術開発を進めていきます。また、産業応用についても、大手半導体メーカーなどに本技術の周知を進める方針です。

関連情報

「プレスリリース①次世代半導体製造向けの極微細穴あけ加工を実現 ―業種横断の協働拠点で先端半導体をけん引―」(2022/10/24)発表者・研究者等情報

- 東京大学

- 物性研究所

- 小林 洋平 教授

- 兼:光量子科学連携研究機構

- 谷 峻太郎 助教(研究当時)

- 乙津 聡夫 特任研究員

- 小林 洋平 教授

- 大学院理学系研究科

- 田丸 博晴 特任教授

- 兼:光量子科学連携研究機構

- 田丸 博晴 特任教授

- 物性研究所

- 味の素ファインテクノ株式会社

- 真子 玄迅 代表取締役社長

- (プロジェクト発足当時:電子材料事業部長)

- 真子 玄迅 代表取締役社長

- 三菱電機株式会社

- 先端技術総合研究所

- 湯澤 隆 産業オートメーションシステム技術部 部長

- 中村 直幸 同 主席研究員

- 先端技術総合研究所

- 岡田 穣治 取締役

学会情報

- 学会名 : ECTC(2024 IEEE 74th Electronic Components and Technology Conference)

- 題名 : Laser micro drilling of around 3 microns into Ajinomoto Build-up Film

- 発表者 : Toshio Otsu, Shuntaro Tani, Shoko Nagayama, Ryo Miyamoto, George Okada, Naoyuki Nakamura, Junichi Nishimae, Hiroharu Tamaru, and Yohei Kobayashi

- URL : https://www.ectc.net/program/74-ECTCAdvance-Web-Final.pdf

研究助成

本研究の一部は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)「高輝度・高効率次世代レーザー技術開発」、戦略的イノベーション創造プログラム(SIP)「光・量子を活用したSociety5.0実現化技術」および光・量子飛躍フラッグシッププログラム(Q-LEAP)「光量子科学によるものづくりCPS化拠点(JPMXS0118067246)」の支援により実施されました。

用語解説

- (注1)半導体後工程 :

- 半導体製造工程のうちチップを作成するのが前工程、チップを実装するのが後工程。

- (注2)パッケージ基板 :

- 半導体チップとプリント配線基板とを電子接続する中間的な基板。半導体の微細な電極間隔からプリント配線基板の配線間隔へ変換する役割。多層構造になっており、各層は絶縁膜にあけた穴を通して電気信号をつないでいます。

- (注3)チップレット :

- 従来は1つのチップでロジック構成要素を一体で製造していましたが、チップの大型化に伴い歩留まりが悪くなってきました。チップレットとは、構成要素ごとに別チップとして製造した上で、パッケージ基板上に組み合わせて実装し一体のパッケージとして動作するよう製造する技術およびその手法。チップレット化により、後工程も含めて半導体の性能向上が期待されています。

- (注4)TACMIコンソーシアム :

- 東京大学が、産学官連携による光ものづくり協創を推進するため2017年10月30日に設立した企業間マッチングのプラットフォーム。大学が有する最先端のレーザー光源や加工機を会員企業に開放し、各企業が持つシーズとニーズを実践的にマッチングさせる役割を果たしています。

公式サイト http://www.utripl.u-tokyo.ac.jp/tacmi/ - (注5)EUV露光 :

- 半導体前工程のハイエンド露光プロセス。波長13.5ナノメートルのEUV光を露光に使うことで7ナノメートル以下のプロセスルールを実現しています。半導体前工程が微細化するための重要技術。

- (注6)ABF (Ajinomoto Build-up Film Ⓡ) :

- PCの心臓部である高性能半導体(CPU)には「味の素ビルドアップフィルムⓇ (ABF)」という層間絶縁材が使われており、現在では全世界の主要なパソコンのほぼ100%のシェアに達しています。

関連ページ

- TACMI 高効率レーザープロセッシング推進コンソーシアム(Consortium for Technological Approaches toward Cool laser Manufacturing with Intelligence)

- 東京大学物性研究所 小林研究室

- 2022.10.24プレスリリース次世代半導体製造向けの極微細穴あけ加工を実現 ―業種横断の協働拠点で先端半導体をけん引―

- 2021.03.01物性研ニュースNEDOの事業成果を集約したプラットフォームを構築 ―レーザー光源や加工機を連携させ、最適な加工条件を探索―

- 2018.10.23プレスリリース極端紫外線レーザーにより熱影響が極めて少ない材料加工を実現 -レーザー加工メカニズムの解明や最適加工の実現に期待-

- 2017.11.27プレスリリース「TACMIコンソーシアム」を設立 -産官学連携で光ものづくり協創を目指す-